# APL3200

Dual-Input, USB/AC Adapter, 1-Cell Li+ Charger with OVP and Thermal Regulation

### Features

- Charge from USB or AC Adapter

- Accurate BATT Regulation Voltage

- Programmable DC Charging Current

- Selectable USB Charging Current (Either 100mA or 500mA)

- Thermal Regulation for Simplified Board Design

- Input Protection Up to 18V

- Soft-Start

- External Thermistor Monitoring

- Charge Shutdown Control

- Charge Status Outputs

- DC and USB Power-OK Indicators

- Small, High Power QFN5x5-16 and TQFN4x4-16 Packages

- Lead Free and Green Devices Available

(RoHS Compliant)

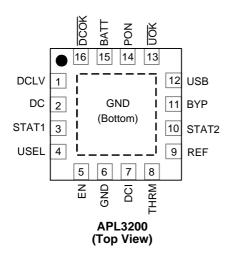

### **Pin Configuration**

### **General Description**

The APL3200 charges a single-cell Li+ battery from both USB and AC adapter sources. It also includes batteryto-input power switchover, therefore, the system can be powered directly from the power source rather than from the battery.

In its simplest application, the APL3200 doesn't need external MOSFET or diodes and accepts input voltages up to 6.5V; however, DC input over-voltage protection up to 18V can be added with a single SOT PFET.

On-chip thermal limiting simplifies PC board layout and allows optimum charging rate without the thermal limits imposed by worst-case battery and input voltage. When the APL3200 thermal limit is reached, the charger does not shut down but simply reduces charging current. Ambient or battery temperature can be monitored with an external thermistor. When the temperature is out of range, charging pauses.

Other features include STAT 1 and STAT 2 outputs indicating various charge status. DC power-OK (DCOK), USB power-OK (UOK), and poweron (PON) outputs indicate when valid power is present. These outputs drive logic or power-selection MOSFETs to disconnect the charging sources from the load and to protect the APL3200 from overvoltage. The APL3200 doesn't contain logic for communication with the USB host. It must receive instructions from a local microcontroller. The APL3200 is available in 16-pin 5mmx5mm QFN and 4mmx4mm TQFN packages and operates over the -40°C to +85°C temperature range.

## **Applications**

- Smart Phones and PDAs

- Wireless Appliances

- Digital Still Camera

- Internet Appliances

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

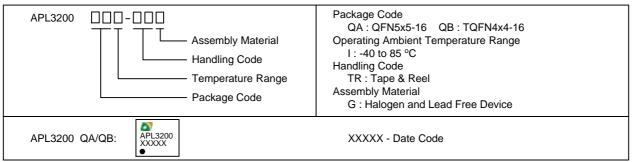

## Ordering and Marking Information

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020C for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).

### Absolute Maximum Ratings (Note 1)

| Symbol           | Parameter                                                   | Rating                        | Unit |

|------------------|-------------------------------------------------------------|-------------------------------|------|

|                  | DC, DCOK to GND                                             | -0.3 ~ 20                     | V    |

|                  | DCLV, USB, BATT, UOK, PON, STAT1, STAT2, EN,<br>USEL to GND | -0.3 ~ 7                      | V    |

| V <sub>BYP</sub> | BYP to GND                                                  | -0.3 ~ 7                      | V    |

|                  | DCI, THRM, REF to GND                                       | -0.3 ~ V <sub>BYP</sub> +0.3V | V    |

|                  | Continuous DCLV Input Current                               | 1.6                           | А    |

|                  | Continuous USB Input Current                                | 0.6                           | А    |

|                  | Maximum Junction Temperature                                | 150                           | °C   |

| T <sub>STG</sub> | Storage Temperature                                         | -65 ~ 150                     | °C   |

| T <sub>SDR</sub> | Maximum Lead Soldering Temperature, 10 Seconds              | 260                           | °C   |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Thermal Characteristics**

| Symbol        | Parameter                               | Typical Value | Unit |

|---------------|-----------------------------------------|---------------|------|

|               | Junction-to-Ambient Resistance (Note 2) |               |      |

| $\theta_{JA}$ | QFN5x5-16                               | 40            | °C/W |

|               | TQFN4x4-16                              |               |      |

Note 2 :  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. The exposed pad of QFN-16 is soldered directly on the PCB.

## **Recommended Operating Conditions**

| Symbol             | Parameter                                   | Range      | Unit |

|--------------------|---------------------------------------------|------------|------|

| V <sub>DC</sub>    | DC Input Voltage (with OVP Protection)      | 4.35 ~ 18  | V    |

| $V_{DC}, V_{DCLV}$ | DCLV Input Voltage (without OVP Protection) | 4.35 ~ 6.0 | V    |

| V <sub>USB</sub>   | USB Input Voltage                           | 4.35 ~ 6.5 | V    |

# **Recommended Operating Conditions (Cont.)**

| Symbol         | Parameter            | Range     | Unit |

|----------------|----------------------|-----------|------|

|                | DCLV Input Current   | ~ 1       | А    |

|                | USB Input Current    | ~ 0.5     | А    |

| T <sub>A</sub> | Ambient Temperature  | -40 ~ 85  | °C   |

| TJ             | Junction Temperature | -40 ~ 125 | °C   |

### **Electrical Characteristics**

Refer to the typical application circuit. These specifications apply over  $V_{USB} = V_{DC} = V_{DCLV} = V_{EN} = V_{USEL} = 5V$ ,  $V_{BATT} = 4.2V$  and  $T_A = -40 \sim 85^{\circ}C$  ( $T_J = -40 \sim 125^{\circ}C$ ), unless otherwise specified. Typical values are at  $T_A = 25^{\circ}C$ .

| Sumbol           | Parameter                                                           | Test Conditions                                                                                                                            |      | Unit |      |      |

|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Symbol           | Parameter                                                           | Test Conditions                                                                                                                            | Min. | Тур. | Max. | Unit |

| SUPPLY C         | URRENT                                                              |                                                                                                                                            | •    | •    |      |      |

| 1                | DC Sunak Current                                                    | $V_{EN} = 0V$                                                                                                                              | -    | 1    | 2    | mA   |

| I <sub>DC</sub>  | DC Supply Current                                                   | V <sub>EN</sub> = 5V, I <sub>CHG_DC</sub> =0A                                                                                              |      | 1    | 2    | mA   |

|                  |                                                                     | $V_{EN} = 0V, V_{DCLV} = 5V, V_{USB} = 0V$                                                                                                 | -    | 300  | 500  | μA   |

| DCLV             | DCLV Supply Current                                                 | $V_{EN} = 5V, V_{DCLV} = 5V, V_{USB} = 0V$                                                                                                 | -    | 2    | 3    | mA   |

|                  |                                                                     | $V_{\text{EN}} = 0V,  V_{\text{USB}} = 5V,  V_{\text{DCLV}} = 0V$                                                                          | -    | 300  | 500  | μA   |

| I <sub>USB</sub> | USB Supply Current                                                  | $\label{eq:VEN} \begin{split} V_{\text{EN}} &= 5V, \ V_{\text{USB}} = 5V, \ V_{\text{DCLV}} = 0V \\ I_{\text{CHG\_USB}} &= 0A \end{split}$ | -    | 2    | 3    | mA   |

|                  |                                                                     | V <sub>USB</sub> <v<sub>DCLV</v<sub>                                                                                                       | -    | 80   | 160  | μA   |

| C POWER          | R-OK VOLTAGE THRESHOLD AND TIM                                      | ING                                                                                                                                        |      |      |      |      |

|                  | Rising DC Power-OK Threshold                                        |                                                                                                                                            | 3.45 | 3.65 | 3.85 | V    |

|                  | DC Power-OK Hysteresis                                              |                                                                                                                                            | 0.1  | 0.15 | 0.2  | V    |

|                  | DC Rising to DCOK Falling and PON Rising (90%)                      | $V_{\text{DC}}$ rising to 5V, $V_{\text{USB}}\text{=}\text{open}$                                                                          | -    | 20   | -    | ms   |

|                  | DC Rising to UOK and PON Going to Open-Drain                        | $V_{DC}$ step to 5V, $V_{USB}$ = 5V                                                                                                        | -    | 10   | -    | ms   |

|                  | DC Falling to DCOK and PON Going to<br>Open-Drain Propagation Delay | V <sub>USB</sub> =0V or 5V                                                                                                                 | -    | 1    | -    | μs   |

| JSB POWE         | ER-OK VOLTAGE THRESHOLD AND TI                                      | MING                                                                                                                                       |      |      |      |      |

|                  | Rising USB Power-OK Threshold                                       |                                                                                                                                            | 3.45 | 3.65 | 3.85 | V    |

|                  | USB Power-OK Hysteresis                                             |                                                                                                                                            | 0.1  | 0.15 | 0.2  | V    |

|                  | USB Rising to UOK Falling and PON Rising                            | $V_{DC}$ =0V, $V_{USB}$ step to 5V                                                                                                         | -    | 20   | -    | ms   |

|                  | USB Falling to UOK and PON Going to<br>Floating Propagation Delay   | V <sub>DC</sub> =0V                                                                                                                        | -    | 1    | -    | μs   |

| HARGING          | POWER-OK VOLTAGE THRESHOLDS                                         | 3                                                                                                                                          |      |      |      |      |

|                  | Rising DCLV Charging Power-OK<br>Threshold                          |                                                                                                                                            | 3.90 | 4.05 | 4.2  | V    |

|                  | DCLV Charging Power-OK Hysteresis                                   |                                                                                                                                            | 0.15 | 0.25 | 0.35 | V    |

|                  | Rising USB Charging Power-OK<br>Threshold                           |                                                                                                                                            | 3.90 | 4.05 | 4.2  | V    |

|                  | USB Charging Power-OK Hysteretic                                    |                                                                                                                                            | 0.15 | 0.25 | 0.35 | V    |

## **Electrical Characteristics (Cont.)**

Refer to the typical application circuit. These specifications apply over  $V_{USB} = V_{DC} = V_{DCLV} = V_{EN} = V_{USEL} = 5V$ ,  $V_{BATT} = 4.2V$  and  $T_A = -40 \sim 85^{\circ}C$  ( $T_J = -40 \sim 125^{\circ}C$ ), unless otherwise specified. Typical values are at  $T_A = 25^{\circ}C$ .

| Symbol               | Parameter                         | Test Conditions                                                                                             |      | APL3200    |      | Unit             |

|----------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|------|------------|------|------------------|

| Symbol               | Farameter                         |                                                                                                             |      | Тур.       | Max. | Unit             |

| BATTERY              | VOLTAGE AND REFERENCE VOLTA       | GE                                                                                                          |      |            |      |                  |

|                      | BATT Regulation Voltage           |                                                                                                             | -    | 4.20       | -    | V                |

|                      | PATT Population Voltage Acquiracy | T <sub>A</sub> =25°C, V <sub>BYP</sub> =4.0~6.5V                                                            | -0.5 | -          | 0.5  | %                |

|                      | BATT Regulation Voltage Accuracy  | T <sub>A</sub> =-40~85°C (T <sub>J</sub> =-40~125°C)                                                        | -1   | -          | 1    | %                |

|                      | BATT Pre-qual Voltage Threshold   |                                                                                                             | 2.8  | 3          | 3.2  | V                |

|                      | Pre-qual Threshold Hysteresis     |                                                                                                             | -    | 70         | -    | mV               |

|                      | REF Regulation Voltage            |                                                                                                             | -    | 3          | -    | V                |

|                      | REF Voltage Accuracy              | I <sub>REF</sub> =0~500μA,T <sub>J</sub> =-40~125 <sup>°</sup> C,<br>V <sub>BYP</sub> =4.0V~6.5V            | -2   | -          | 2    | %                |

|                      | REF Maximum Output                | REF=GND                                                                                                     | -    | 1.5        | -    | mA               |

| BATTERY              | CHARGING AND PRECHARGING CUI      | RRENT                                                                                                       |      |            |      |                  |

| I <sub>CHG_DC</sub>  | DC Charging Current Range         | I <sub>CHG_DC</sub> =K <sub>SET</sub> x V <sub>SET</sub> / R <sub>SET</sub> ,<br>Without thermal regulation | 100  | -          | 1500 | mA               |

| $V_{\text{SET}}$     | DCI Regulation Voltage            | Without thermal regulation                                                                                  | -    | 1          | -    | V                |

|                      | DCI Regulation Voltage Accuracy   | T <sub>J</sub> =-40~125 <sup>°</sup> C, V <sub>BYP</sub> =4.0~6.5V                                          | -1   | -          | 1    | %                |

|                      | Maximum DCI Output Current        | DCI=GND                                                                                                     | -    | 1.8        | -    | mA               |

| K <sub>SET</sub>     | Charging Current Set Factor       | 100mA≤I <sub>CHG_DC</sub> ≤1A                                                                               | 940  | 1000       | 1060 | -                |

|                      |                                   | V <sub>USEL</sub> =0V                                                                                       | 70   | 82         | 95   | mA               |

| I <sub>CHG_USB</sub> | USB Charging Current              | V <sub>USEL</sub> =5V                                                                                       | 400  | 450        | 495  | mA               |

|                      | Pre-qual charging Current         | V <sub>BATT</sub> = 0 ~ 3V                                                                                  | 35   | 55         | 70   | mA               |

|                      |                                   | DC Input, falling charging current<br>(% of charger current set at DCI)                                     | 8    | 12.5       | 19   | %                |

|                      |                                   | Hysteresis                                                                                                  | -    | 12.5       | -    | %                |

|                      | Charge-Done<br>Current Threshold  | USB Input, V <sub>USEL</sub> =5V, Falling<br>charging current<br>(% of USB charger current)                 | 20   | 25         | 30   | %                |

|                      |                                   | Hysteresis                                                                                                  | -    | 25         | -    | %                |

|                      |                                   | USB Input, V <sub>USEL</sub> =0V                                                                            | In   | Voltage Mo | ode  | -                |

| DROPOUT              | VOLTAGES                          |                                                                                                             |      |            |      |                  |

|                      | DCLV to BATT Dropout Voltage      | $I_{CHG_DC}$ =1A, $V_{DCLV}$ =5V                                                                            | -    | 250        | 450  | mV               |

|                      | USB to BATT Dropout Voltage       | $I_{CHG_USB}$ =450mA, $V_{USB}$ =5V                                                                         | -    | 140        | 250  | mV               |

|                      | DCLV to BYP Dropout Voltage       | I <sub>DCLV-to-BYP</sub> =5mA, V <sub>DCLV</sub> =5V                                                        | -    | 300        | -    | mV               |

|                      | USB to BYP Dropout Voltage        | $I_{USB-to-BYP}=5mA, V_{USB}=5V, V_{DCLV}=0V$                                                               | -    | 300        | -    | mV               |

| THERMIST             | OR MONITOR AND DIE TEMPERATU      | RE REGULATION                                                                                               |      |            |      |                  |

|                      | THRM Cold Trip Level              | V <sub>THRM</sub> rising                                                                                    | 0.79 | 0.81       | 0.82 | $V_{REF}$        |

|                      | THRM Cold Trip Level Hysteresis   |                                                                                                             | -    | 0.03       | -    | $V_{REF}$        |

|                      | THRM Hot Trip Level               | V <sub>THRM</sub> falling                                                                                   | 0.28 | 0.29       | 0.30 | V <sub>REF</sub> |

|                      | THRM Hot Trip Level Hysteresis    |                                                                                                             | -    | 0.03       | -    | V <sub>REF</sub> |

|                      | Die Thermal Regulation Limit      |                                                                                                             | -    | 120        | -    | °C               |

|                      | THRM Disable Voltage Threshold    |                                                                                                             | 50   | 100        | 150  | mV               |

# **Electrical Characteristics (Cont.)**

Refer to the typical application circuit. These specifications apply over  $V_{USB} = V_{DC} = V_{DCUV} = V_{EN} = V_{USEL} = 5V$ ,  $V_{BATT} = 4.2V$  and  $T_A = -40 \sim 85^{\circ}C$  ( $T_J = -40 \sim 125^{\circ}C$ ), unless otherwise specified. Typical values are at  $T_A = 25^{\circ}C$ .

| 0               | Bananatan                                      | Test Osmilitisms                                                                                                      |      | APL3200 |      | 11   |

|-----------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|---------|------|------|

| Symbol          | Parameter                                      | Parameter Test Conditions                                                                                             |      | Тур.    | Max. | Unit |

| SOFT-STA        | RT, DC OVER-VOLTAGE VOLTAGE T                  | RESHOLD, AND REVERSE CUR                                                                                              | RENT |         |      |      |

| T <sub>ss</sub> | Soft-Start Interval                            | I <sub>CHG</sub> =0A to fast-charging current                                                                         | 4    | 7       | 12   | ms   |

|                 | Rising DC Over-Voltage Threshold               |                                                                                                                       | 6.2  | 6.4     | 6.6  | V    |

|                 | BATT Input Current                             | $V_{DCLV}=V_{USB}=0V, V_{BATT}=4.2V$                                                                                  | -    | -       | 8    | μA   |

|                 | BATT Shutdown Input Current                    | $V_{\text{EN}} = \! 0 V,  V_{\text{DCLV}} \text{ and/or } V_{\text{USB}} \! = \! 5 V,  V_{\text{BATT}} \! = \! 4.2 V$ | -    | -       | 4    | μΑ   |

| LOGIC INP       | UT/OUTPUTS AND GATE DRIVERS                    |                                                                                                                       |      |         |      |      |

|                 | PON Pull-High Resistance                       | PON pulled up to BYP                                                                                                  | -    | 10      | -    | Ω    |

|                 | PON Pull-low Resistance                        | PON pulled to GND, $V_{DCLV}=V_{USB}=0V$                                                                              | -    | 140     | -    | kΩ   |

|                 | DCOK, UOK, STAT1, STAT2 Pull-low<br>Resistance | All pins pulled to GND                                                                                                | -    | 10      | -    | Ω    |

|                 | DCOK Off-Leakage Current                       | V <sub>DCOK</sub> =12V, VDC=0V                                                                                        | -    | -       | 1    | μA   |

|                 | UOK Off-Leakage Current                        | V <sub>UOK</sub> =5V, VDC=5V                                                                                          | -    | -       | 1    | μΑ   |

|                 | STAT1, STAT2 Off-Leakage Current               | V <sub>STAT1,2</sub> =5V, V <sub>DC</sub> =V <sub>USB</sub> =0V                                                       | -    | -       | 1    | μA   |

|                 | EN, USEL Logic-Input High Level                | T <sub>J</sub> =-40~125 <sup>°</sup> C, rising                                                                        | 1.6  | -       | -    | V    |

|                 | EN, USEL Logic-Input Low Level                 |                                                                                                                       | -    | -       | 0.4  | V    |

|                 | EN, USEL Input Bias Current                    |                                                                                                                       | -    | -       | 1    | μA   |

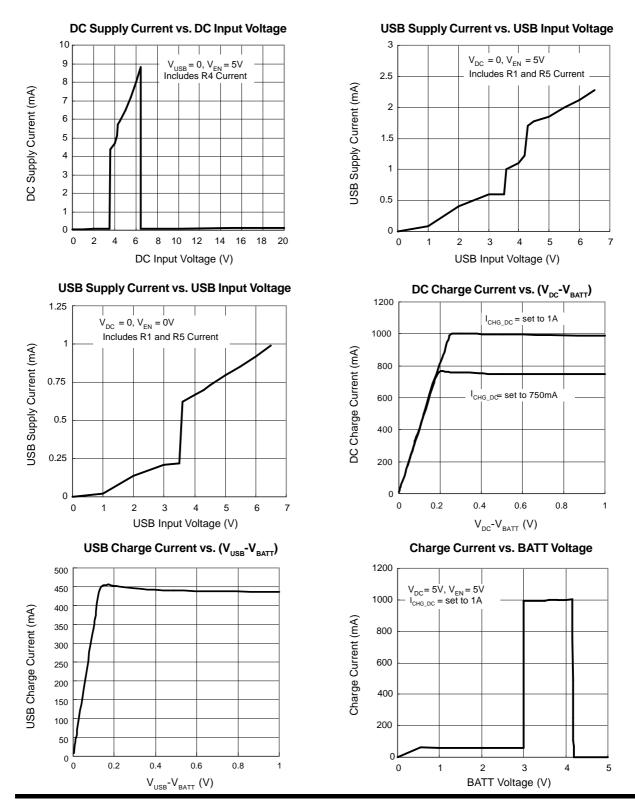

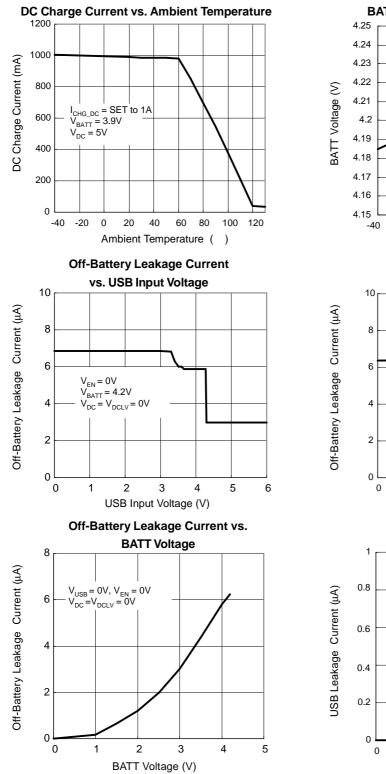

### **Typical Operating Characteristics**

$(V_{\text{USB}}=V_{\text{DC}}=V_{\text{DCLV}}=V_{\text{EN}}=5V, V_{\text{BATT}}=4.2V, V_{\text{THRM}}=V_{\text{REF/2}}, V_{\text{USEL}}=5V, \text{Typical Application Circuit 3, } T_{\text{A}}=25^{\circ}\text{C}, \text{ unless otherwise noted})$

6

Copyright © ANPEC Electronics Corp. Rev. A.5 - Apr., 2009

www.anpec.com.tw

## **Typical Operating Characteristics (Cont.)**

$(V_{USB} = V_{DC} = V_{DCLV} = V_{EN} = 5V, V_{BATT} = 4.2V, V_{THRM} = V_{REF/2}, V_{USEL} = 5V, Typical Application Circuit 3, T_A = 25^{\circ}C, unless otherwise noted)$

7

www.anpec.com.tw

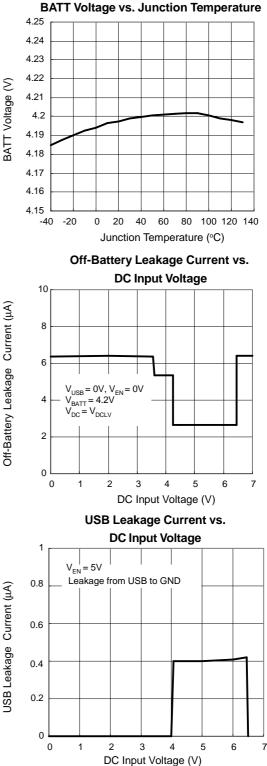

### **Operating Waveforms**

| LeCroy |      | -    |   |      |      |   |

|--------|------|------|---|------|------|---|

|        | <br> | <br> |   | <br> | <br> | i |

|        |      |      |   |      |      |   |

|        | <br> | <br> | _ | <br> | <br> | 2 |

|        |      | -    |   |      |      |   |

|        |      | -    | - |      |      | 3 |

|        | <br> | <br> |   | <br> | <br> |   |

|        |      |      | - |      |      | 4 |

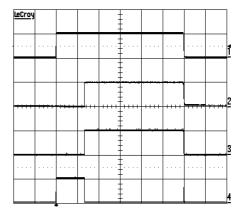

#### **Response to Overvoltage Input**

$$\label{eq:V_USB} \begin{split} & \mathsf{V}_{\mathsf{USB}} {=} \mathsf{0} \mathsf{V} \\ & \mathsf{CH1:} \ \mathsf{V}_{\mathsf{DC}} \ (20 \mathsf{V}/\mathsf{div}) \\ & \mathsf{CH2:} \ \mathsf{V}_{\mathsf{DCLV}} \ (5 \mathsf{V}/\mathsf{div}) \\ & \mathsf{CH3:} \ \mathsf{V}_{\mathsf{PON}} \ (5 \mathsf{V}/\mathsf{div}) \\ & \mathsf{CH4:} \ \mathsf{V}_{\mathsf{DCCR}} \ (20 \mathsf{V}/\mathsf{div}) \\ & \mathsf{Time:} \ 50 \mathsf{ms}/\mathsf{div} \end{split}$$

#### **DC Connect Waveforms**

#### **DC Connect Waveforms**

$\begin{array}{l} \mathsf{V}_{\mathsf{USB}}=\!\!\mathsf{OV}, \ \mathsf{V}_{\mathsf{BATT}}\!\!=\!\!3.9\mathsf{V} \\ \mathsf{CH1}: \ \mathsf{V}_{\mathsf{DC}}(\mathsf{5V/div}) \\ \mathsf{CH2}: \ \mathsf{V}_{\mathsf{DCLV}}(\mathsf{5V/div}) \\ \mathsf{CH3}: \ \mathsf{V}_{\mathsf{PON}}(\mathsf{5V/div}) \\ \mathsf{CH4}: \ \forall_{\mathsf{DOCK}}(\mathsf{20V/div}) \\ \mathsf{Time}: \mathsf{20ms/div} \end{array}$

#### **USB Connect Waveforms**

$\begin{array}{l} {\sf V}_{\rm DC} = \! 0{\sf V}, \, {\sf V}_{\rm BATT} \! = \! 3.9{\sf V} \\ {\sf CH1:} \, {\sf V}_{\rm USB} \, (5{\sf V}/di{\sf v}) \\ {\sf CH2:} \, {\sf V}_{\rm PON} \, (5{\sf V}/di{\sf v}) \\ {\sf CH3:} \, {\sf V}_{\overline{\rm UOK}} \, (5{\sf V}/di{\sf v}) \\ {\sf CH4:} \, {\sf I}_{{\sf CHG}\_{\sf USB}} \, (0.5{\sf A}/di{\sf v}) \\ {\sf Time:} \, 20{\sf ms}/di{\sf v} \end{array}$

## **Operating Waveforms (Cont.)**

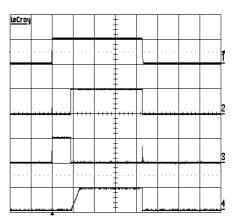

#### **Enable in Fast Charge**

| <u>LeCroy</u> |      | -    | -     |      |      |   |

|---------------|------|------|-------|------|------|---|

|               | <br> | <br> | -<br> | <br> | <br> |   |

|               |      | -    | -     |      |      | Ľ |

|               |      | -    | -     |      | <br> |   |

|               | <br> | <br> |       | <br> | <br> | 2 |

|               | <br> | <br> | -     | <br> | <br> |   |

|               |      | -    |       |      |      | 3 |

|               | <br> | <br> |       | <br> | <br> |   |

|               | /    | -    | -     |      |      |   |

$$\begin{split} & \mathsf{V}_{\text{BATT}} = 3.9\mathsf{V}, \ \mathsf{V}_{\text{DC}} = 5\mathsf{V} \\ & \mathsf{CH1:} \ \mathsf{V}_{\text{EN}} \left( 5\mathsf{V} / \text{div} \right) \\ & \mathsf{CH2:} \ \mathsf{V}_{\text{STATE1}} \left( 5\mathsf{V} / \text{div} \right) \\ & \mathsf{CH3:} \ \mathsf{V}_{\text{STATE2}} \left( 5\mathsf{V} / \text{div} \right) \\ & \mathsf{CH4:} \ \mathsf{I}_{\text{CHG_DC}} (1\mathsf{A} / \text{div}) \\ & \mathsf{Time:} \ 20\mathsf{ms} / \text{div} \end{split}$$

#### **Enable in Precharge**

$$\begin{split} & \mathsf{V}_{\mathsf{BATT}} = 2.7\mathsf{V}, \ \mathsf{V}_{\mathsf{DC}} = 5\mathsf{V} \\ & \mathsf{CH1:} \ \mathsf{V}_{\mathsf{EN}} \left( 5\mathsf{V}/\mathsf{div} \right) \\ & \mathsf{CH2:} \ \mathsf{V}_{\mathsf{STATE1}} \left( 5\mathsf{V}/\mathsf{div} \right) \\ & \mathsf{CH3:} \ \mathsf{V}_{\mathsf{STATE2}} \left( 5\mathsf{V}/\mathsf{div} \right) \\ & \mathsf{CH4:} \ \mathsf{I}_{\mathsf{CHG_DC}} (5\mathsf{OmA}/\mathsf{div}) \\ & \mathsf{Time:} \ 2\mathsf{OmS}/\mathsf{div} \end{split}$$

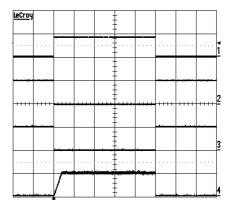

#### **Enable in Charge Done**

| <u>LeCroy</u> |      | -     |   |      |      |   |

|---------------|------|-------|---|------|------|---|

| • • • • •     | <br> | <br>  |   | <br> | <br> | 1 |

|               |      | -     |   |      |      |   |

|               | <br> | <br>  |   | <br> | <br> | 2 |

|               | <br> | <br>- |   |      | <br> | ſ |

|               |      | <br>- | - |      |      | 3 |

|               | <br> | <br>  |   | <br> | <br> |   |

|               |      |       |   |      |      | 4 |

# **Pin Description**

| F   | PIN   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1   | DCLV  | DC charger power input from an AC adapter. DCLV charges BATT through an internal MOSFET. Maximum operating voltage at this pin is 6.0V. When an over-voltage protection MOSFET is connected, DCLV is connected to DC when the input voltage is suitable for charging.                                                                                                                                                            |

| 2   | DC    | Voltage-Sense Pin for DC Input from AC Adapter. Maximum operating voltage at this pin is 18V. This voltage-sense function provides status of DC voltage from AC adapter for over-voltage protection.                                                                                                                                                                                                                             |

| 3   | STAT1 | Charge status output pin 1. This pin is an active-high, open-drain output pin.                                                                                                                                                                                                                                                                                                                                                   |

| 4   | USEL  | USB charging current selection input. USEL is a logic input that sets USB source charging current to 500mA when USEL is logic high and to 100mA when USEL is logic low.                                                                                                                                                                                                                                                          |

| 5   | EN    | Charging enable/disable control pin. Drive EN high to enable the device. When EN is low, the charger stops charging and DCOK, UOK, and PON remain active.                                                                                                                                                                                                                                                                        |

| 6   | GND   | Signal and power ground.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7   | DCI   | DC charging current setting pin. Connecting a resistor to the GND sets the fast-charge current when the DCLV input is powering the charger.                                                                                                                                                                                                                                                                                      |

| 8   | THRM  | External thermistor connection pin. THRM pauses charging when an externally connected the thermistor (10k $\Omega$ at +25°C) is at less than 0°C or greater than +50°C. Connecting this pin to the GND disables this function.                                                                                                                                                                                                   |

| 9   | REF   | $3V$ Reference voltage output pin. Sources up to 1.5mA to bias the external thermistor. Bypass with 0.1 $\mu$ F to the GND. REF loading does not affect BATT regulation accuracy.                                                                                                                                                                                                                                                |

| 10  | STAT2 | Charge status output pin 2. This pin is an active-high, open-drain output pin.                                                                                                                                                                                                                                                                                                                                                   |

| 11  | BYP   | Bias supply pin for internal circuitry. This pin switches to the pin (either DCLV or USB) with higher supply than the other. Bypass with a $2.2\mu$ F capacitor to the GND.                                                                                                                                                                                                                                                      |

| 12  | USB   | USB charger power input. Charge BATT through an internal MOSFET.                                                                                                                                                                                                                                                                                                                                                                 |

| 13  | UOK   | USB power-ok output pin. $\overline{\text{UOK}}$ is an active-low, open-drain output that goes low when USB is the valid charging source (V <sub>USB</sub> >3.65V and V <sub>DC</sub> <3.65V).                                                                                                                                                                                                                                   |

| 14  | PON   | Gate driver output pin for the P-channel MOSFET disconnecting battery from system load when power is applied. PON is an active-high, open-drain output with an internal 140k $\Omega$ resistor to the ground that goes high when V <sub>DC</sub> or V <sub>USB</sub> is ready.                                                                                                                                                   |

| 15  | BATT  | Charger output pin. Connect this pin to the positive terminal of a Li+ battery.                                                                                                                                                                                                                                                                                                                                                  |

| 16  | DCOK  | DC power-ok output pin. $\overline{\text{DCOK}}$ is an active-low, open-drain output that goes low when $3.65\text{V} < \text{V}_{\text{DC}} < 6.4\text{V}$ .                                                                                                                                                                                                                                                                    |

| Pad | EP    | Exposed metal pad. This pad is connected to the ground. Note this internal connection is a soft-connect, meaning there is no internal metal or bond wire physically connecting the exposed pad to the GND pin. The connection is through the silicon substrate of the die and then through a conductive epoxy. Connecting the exposed pad to the ground does not remove the requirement for a good ground connection to the GND. |

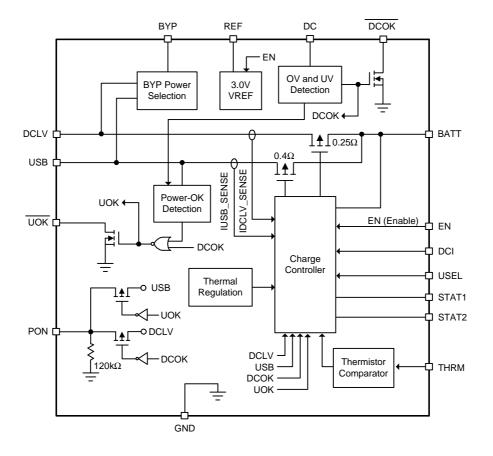

## **Block Diagram**

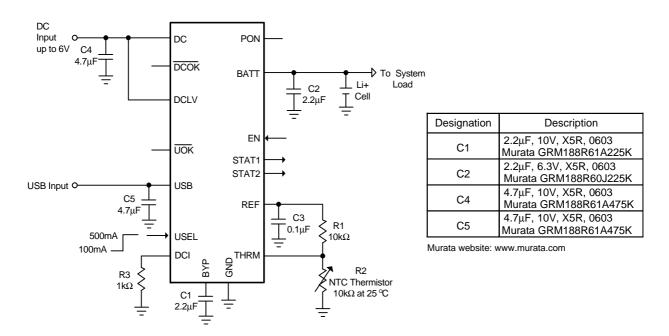

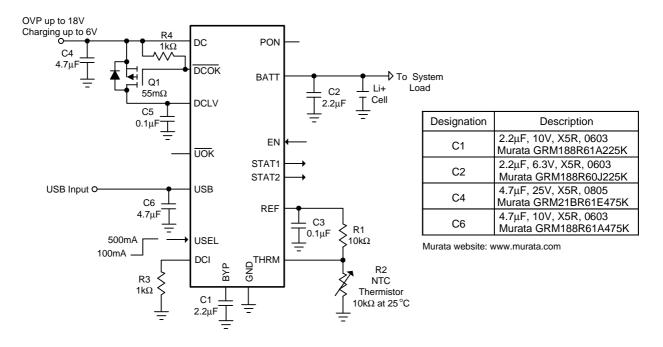

## **Typical Application Circuits**

1. A Minimal Circuit that Assumes System Load Is Only Connected to the Battery. The circuit has a 6.0V maximum input and disables charging for inputs over 6.4V.

2. A circuit with overvoltage protection MOSFET (Q1) on DC input withstands up to 18V from the AC adapter and disables charging at inputs over 6.4V.

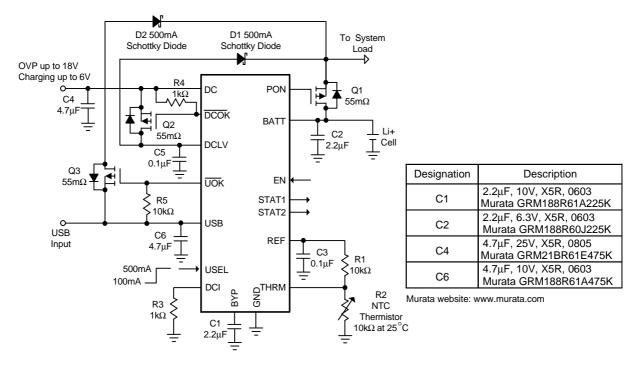

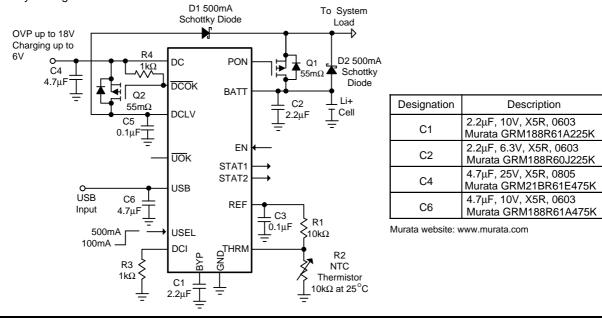

### **Typical Application Circuits (Cont.)**

3. Full-Featured Circuit. Overvoltage protection MOSFET (Q2) on DC withstands up to 18V from the AC adapter, but disables charging at inputs over 6.4V. Output switch-over MOSFET (Q1) disconnects the battery from the system load when input power is applied. The input can power the system through D1, D2, Q2, and Q3 when either USB or AC power is present.

4. Partial-Battery Load Switching. AC adapter power is routed directly to system load, but USB power is not. When USB power is connected, total USB current is limited to that set by USEL and system power is drawn from the battery through D2.

Copyright © ANPEC Electronics Corp. Rev. A.5 - Apr., 2009 www.anpec.com.tw

### **Function Description**

#### **Autonomous Power Source Selection**

The APL3200 charges a single-cell Li+ battery from either USB power sources or AC adapter sources. The APL3200 includes voltage sensing, monitoring the voltage on the DC pin, and switchover circuitry that selects the active input source to supply charging current. When both inputs are active, priority is given to the AC adapter. Table 1 describes the switchover between AC adaptor and USB power sources.

| DC                   | USB                    | Description          |

|----------------------|------------------------|----------------------|

| V <sub>DC</sub> >18V | V <sub>USB</sub> <6.5V | Exceeds operating in |

Table 1 USB and DC Input Selection

| V <sub>DC</sub> >18V         | V <sub>USB</sub> <6.5V | Exceeds operating input |  |

|------------------------------|------------------------|-------------------------|--|

| V <sub>DC</sub> <18V         | V <sub>USB</sub> >6.5V | range. Not allowed.     |  |

| 4V <v<sub>DC&lt;6.4V</v<sub> | V <sub>USB</sub> <6.5V | DCLV supplies charging  |  |

| 4v <v<sub>DC&lt;0.4v</v<sub> | VUSB<0.5V              | current.                |  |

| $V_{DC}$ <4V or              | V <sub>USB</sub> >4V   | USB supplies charging   |  |

| V <sub>DC</sub> >6.4V        | VUSB>4V                | current.                |  |

| $V_{DC}$ <4V or              | Vuse<4V                | No oborging             |  |

| V <sub>DC</sub> >6.4V        | VUSB<4V                | No charging.            |  |

When power is connected to DC, the APL3200 requires 20ms to validate the input. Consequently, charging is interrupted for 20ms until it is determined that input power is good. Also, when DC power is removed while valid USB power is present, charging is interrupted for 20ms before transferring to the USB source.

An additional power selection circuit selects one of the power sources for control circutry of APL3200. The higher voltage on either DCLV or USB supplies control circutry with bias current through the selected internal MOSFET connected from DCLV or USB to BYP. BYP is the bypass connection for the APL3200's internal power rail. Bypass to the GND with a  $2.2\mu$ F or greater capacitor to reduce voltage ripple.

#### Enable (EN)

The enable input, EN, switches the charging of APL3200 on or off. With EN high, the APL3200 can begin charging. When EN is low, DCOK and PON remain active. Charging stops when EN is low, but the chip remains biased and continues to draw current from the input supplies. Therefore, power-monitoring outputs can remain valid.

#### DC Power-OK (DCOK)

DCOK is an active-low and open-drain output that goes low when  $V_{DC}$  is below 6.4V and above 3.65V. DCOK can be used as a logic output or to drive an external P-channel MOSFET. This allows the charger to protect the input from over-voltage up to 18V. Charging from AC adaptor is disabled for inputs over 6.4V. An external 1k $\Omega$  pull-up resistor keeps DCOK high (external MOSFET off) until it is the certain voltage within the acceptable range. To verify that the input voltage is stable, DCOK has an internal delay of 20ms before connecting power to DCLV. DCOK remains operational when EN is low (charger off).

#### USB Power-OK ( UOK)

$\overline{\text{UOK}}$  is an active-low and open-drain output that goes low to indicate that V<sub>USB</sub> is valid (greater than 3.65V).  $\overline{\text{UOK}}$ remains operational when EN is low (charger off). An external 10k $\Omega$  pullup resistor keeps  $\overline{\text{UOK}}$  high until it is certain that power is within the acceptable range for 20ms.  $\overline{\text{UOK}}$  can be used as a logic output, or to control a MOSFET that switches USB power directly to the system load when the APL3200 is powered from a USB source.

#### Power On (PON)

PON goes high when  $V_{DC}$  or  $V_{USB}$  is within its normal operating range(3.65V<V\_{DC}<6.4V or  $V_{USB}$ >3.65V) to turn off the external P-channel MOSFET, disconnecting the battery from system load. Also, PON can be used as a logic output to indicate power is connected.

The PON has an internal 10 $\Omega$  MOSFET for pulling up to BYP voltage and an internal 120k $\Omega$  resistor for pulling down to the GND.

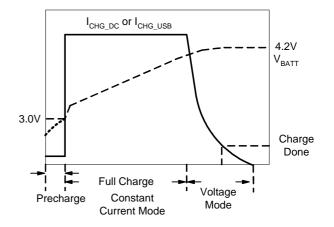

#### Precharge Current

When the APL3200 is powered with a battery connected, the IC first detects if the cell voltage is ready for full charge current. If the cell voltage is less than the prequal level (3V typ.), the battery is precharged with a 50mA current until the cell reaches the proper level. The full charging current, as set by USEL or DCI, is then applied.

## Function Description (Cont.)

#### **USB Charging Current**

The charging current from the USB source is selected by USEL. A USB source can supply a maximum of 100mA or 500mA. USB hosts and powered hubs typically supply 500mA while unpowered hubs supply 100mA. A logic low on USEL selects a 100mA maximum charging current. A logic high on USEL selects a 500mA maximum charging current.

#### **DC Charging Current**

When charging from the DCLV input, the DCI voltage ( $V_{SET}$ ) and the resistor ( $R_{SET}$ ) connected from this pin to the GND set the charging current ( $I_{CHG_{DC}}$ ) as the following equation :

$$\mathsf{I}_{\mathsf{CHG}_\mathsf{DC}} = \mathsf{K}_{\mathsf{SET}} \times \frac{\mathsf{V}_{\mathsf{SET}}}{\mathsf{R}_{\mathsf{SET}}}$$

The charging current set factor  $(K_{SET})$  is shown in the Electricl Characteristics. The DCI regulation voltage is reduced by thermal regulation function. Connecting DCI to the GND results in a limited 1.8A charging current.

#### **Battery Full Indication**

The APL3200 reports the charge-done status on STAT1 and STAT2 pins when the charging current falls below a percentage of the set fast-charge current (Table 2) and the charger is in voltage mode ( $V_{BATT}$  near 4.2V).

| CHARGING SOURCE                    | CHARGE-DONE<br>CURRENT THRESHOLD                         |

|------------------------------------|----------------------------------------------------------|

| DCLV Charging                      | 12.5% of Fast-charge current and charger in voltage mode |

| USB Charging<br>(500mA, USEL=high) | 125mA and charger in voltage mode                        |

| USB Charging<br>(100mA, USEL=low)  | Charger in voltage mode                                  |

Table 2 Battery Full Indication

When charging from a DC source, charge-done occurs when  $I_{CHG_{DC}}$  falls to 12.5% of the current set by  $R_{SET}$  and the charger is in voltage mode ( $V_{BATT}$  near 4.2V). When charging from a USB source with USEL high, charge-done occurs when  $I_{CHG_{USB}}$  falls to 125mA and the charger

is in voltage mode. If the APL3200 is charging from a USB source with USEL low, charge-done occurs when the charger enters voltage mode.

After the APL3200 enunciates the charge-done signal, it keeps operating in voltage mode without turning off the charger and stopping the safety counter.

#### **Thermal Regulation**

On-chip thermal limiting in the APL3200 simplifies PC board layout and allows charging rates to be automatically optimized without constraints imposed by worstcase minimum battery voltage, maximum input voltage, and maximum ambient temperature. When the APL3200 thermal limit is reached, the charger does not shut down but simply reduces charging current. This allows the board design to be optimized for compact size and typical thermal conditions. The APL3200 reduces charging current to keep its die temperature below +120°C. The APL3200's QFN package includes a bottom metal plate that reduces thermal resistance between the die and the PC board. The external pad should be soldered to a large ground plane. This helps dissipate power and keeps the die temperature below the thermal limit. The APL3200's thermal regulator is set for a +120°C die temperature.

#### **External Thermistor Monitor (THRM)**

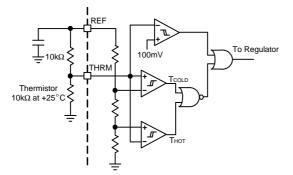

The APL3200 features an internal window comparator to monitor battery pack temperature or ambient temperature with an external negative temperature coefficient thermistor. In typical systems, temperature is monitored to prevent charging at ambient temperature extremes (below 0°C or above +50°C). When the temperature moves outside these limits, charging is stopped. If the  $V_{\text{THERM}}$  returns to its normal window, charging resumes. Connect THRM to the GND when not using this feature. The THRM block diagram is detailed in Figure 1. Note that the temperature monitor at THRM entirely separates from the on-chip temperature limiting discussed in the THRM input are 0.74 x  $V_{\text{REF}}$  for the COLD trip point and 0.29 x  $V_{\text{REF}}$  for the HOT trip point.

## Function Description (Cont.)

#### External Thermistor Monitor (THRM) (Cont.)

Figure 1. Thermistor Sensing Block Diagram

#### **Sleep Mode**

The APL3200 charger circuitry enters the low-power sleep mode if both AC adapter and USB power are removed from the circuit. This feature prevents draining the battery into the APL3200 during the absence of input supplies. Note that in sleep mode, PON remains low in order for the battery to continue supplying power to the system load.

| Table 3 Status Pin St | ummary |

|-----------------------|--------|

|-----------------------|--------|

| CHARGE STATE            | STAT1 | STAT2 |

|-------------------------|-------|-------|

| Precharge in progress   | ON    | ON    |

| Fast charge in progress | ON    | OFF   |

| Charge done             | OFF   | ON    |

| Charge suspended        | OFF   | OFF   |

| Sleep mode              | OFF   | OFF   |

#### **Charge Status Outputs**

The open-drain STAT1 and STAT2 outputs indicate various charger operations are shown in Table 3. These status pins can be used to drive LEDs or communicate to the host processor. Note that OFF indicates the open-drain transistor is turned off. Note that this assumes EN=High.

#### Soft-Start

The APL3200 is equipped with a soft-start function to control the rise rate of the charging current rising from zero to the fast-charging current level in constant current mode. During DC charger soft-start, the APL3200 ramps up the voltage on DCI pin with constant well-controlled slew rate. The charging current is proportional to the DCI voltage.

The soft-start interval is 7 ms (typical) and is independent of the fast -charging current level.

Figure 2. Typical Charging Profile

### **Application Information**

#### Input Overvoltage Protection Switch

Connect a P-channel MOSFET between DCLV and DC to protect the DCLV input pin from over-voltage up to 18V. When DC voltage is above 6.4V OVP threshold, the DCOK will be pulled high to turn off the P-channel MOSFET. The P-channel MOSFET will be turned on again until the DC voltage is below the OVP threshold. If the OVP function is not needed, leave the DCOK open and tie the DC pin to DCLV pin.

#### **Battery-Load Switch**

When an AC adapter or USB power is connected to charger, some systems prefer that system load is supplied from the AC adapter or USB power rather than from the battery. In these systems, the battery is permanently connected to system load. If the battery is completely discharged, the system might not ready to operate immediately. If the battery-load switch function is needed, uses external components D1, D2, Q1, Q2, and Q3 to achieve the function.

Typical Application Circuit 3 shows the full-featured circuit. When input power is supplied, the Q1 disconnects the battery from the system load. The input can power the system through D1, D2, Q2, and Q3 when either USB or AC power is present. Typical Application Circuit 4 shows the partial battery-load switching. AC adapter power is routed directly to the battery but USB power is not. When the USB power is connected, total USB current is set by USEL and system power is drawn from the battery through D2.

#### STAT Pins

The STAT1 and STAT2 outputs indicate various charge status. These two pins can be used to drive LEDs or communicate to the host processor. When status pins

are monitored by a processor, there should be a  $10k\Omega$  pull-up resistor to connect each status pin and the V<sub>cc</sub> of the processor; furthermore, when the status is viewed by LED, the LED with a current rating is less than 10mA and a resistor should be selected to connect LED in series, so the current will be limited to the desired current value. The resistor is calculated by the following equation:

$$\mathsf{R}_{\mathsf{LED}} = \frac{(\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{LED}} - \mathsf{ON})}{\mathsf{P}_{\mathsf{D}}}$$

In other words, the LED and resistor between the input and each status pin shoule in series.

#### **Capacitor Selection**

Typically, a  $4.7\mu$ F ceramic capacitor is used to connect from DC/USB to the GND. For high charging current, it is recommended to use a larger input bypass capacitance to reduce supply noise. Note that if the OVP function is used, the DC should protect against the high DC input voltage, so the voltage rating of the DC input capacitor must be larger than 25V.

There is a ceramic capacitor connecting from BATT to the GND for proper stability. To work well with most applications, at least a  $2.2\mu$ F X5R ceramic capacitor is required.

#### **Thermal Consideration**

The APL3200 is available in a thermally enhanced QFN package with an exposed pad. It is recommended to connect the exposed pad to a large copper ground plane on the backside of the circuit board through several thermal vias for heatsinking. The exposed pad transfers heat away from the device, allowing the APL3200 to charge the battery with maximum current while minimizing the increase in die temperature.

The most common measure of package thermal performance is thermal resistance measured from the device junction to the air surrounding the package surface ( $\theta_{in}$ ).

The  $\theta_{_{J\!A}}$  can be calculated by the following equation:

$$\theta_{JA} = \frac{T_J - T_A}{P_D}$$

where:

$T_{J}$ =device junction temperature  $T_{A}$ = ambient temperature  $P_{D}$ =device power dissipation

The device power dissipation,  $P_{p}$ , is the function of the charge rate and the voltage drop across the internal FET. It can be calculated by the following equation:

# **Application Information (Cont.)**

#### **Thermal Consideration (Cont.)**

$\mathsf{P}_{\mathsf{D}} = (\mathsf{V}_{\mathsf{DCLV}} - \mathsf{V}_{\mathsf{BATT}}) \times \mathsf{I}_{\mathsf{CHG}_{\mathsf{DC}}} \text{ (or } \mathsf{I}_{\mathsf{CHG}_{\mathsf{USB}}})$

#### **PCB Layout Consideration**

The APL3200 is packaged in a thermally enhanced QFN package. The package includes a thermal pad to provide an effective thermal contact between the device and the printed circuit board. Connecting the exposed pad to a large copper ground plane on the backside of the circuit board through several thermal vias for heatsinking is recommended. Connecting the battery to BATT as close to the device as possible provides accurate battery voltage sensing. All decoupling capacitors and filter capacitors should be placed as close as possible to the device. The high-current charge paths into DC, DCLV, USB, and from the BATT pins must short and wide to minimize voltage drops.

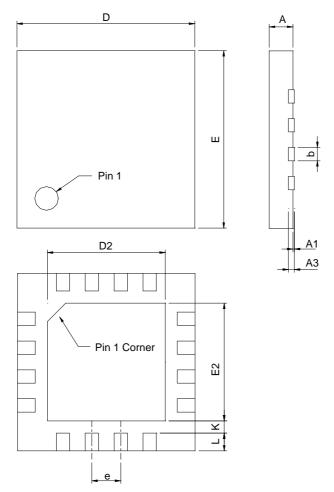

# Package Information

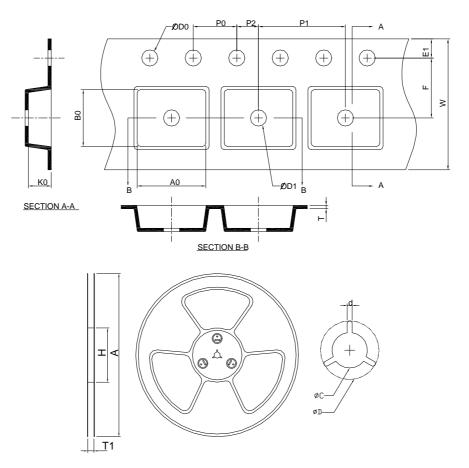

QFN5x5-16

| Ş       | QFN5x5-16 |       |         |       |  |

|---------|-----------|-------|---------|-------|--|

| SY-MBOL | MILLIM    | ETERS | INCHES  |       |  |

| ē       | MIN.      | MAX.  | MIN.    | MAX.  |  |

| А       | 0.80      | 1.00  | 0.031   | 0.039 |  |

| A1      | 0.00      | 0.05  | 0.000   | 0.002 |  |

| A3      | 0.20      | REF   | 0.008 F | REF   |  |

| b       | 0.25      | 0.35  | 0.010   | 0.014 |  |

| D       | 4.90      | 5.10  | 0.193   | 0.201 |  |

| D2      | 3.10      | 3.60  | 0.122   | 0.142 |  |

| Е       | 4.90      | 5.10  | 0.193   | 0.201 |  |

| E2      | 3.10      | 3.60  | 0.122   | 0.142 |  |

| е       | 0.80      | BSC   | 0.031 E | BSC   |  |

| L       | 0.35      | 0.60  | 0.014   | 0.024 |  |

| к       | 0.20      |       | 0.008   |       |  |

Note : 1. Followed from JEDEC MO-220 VHHB.

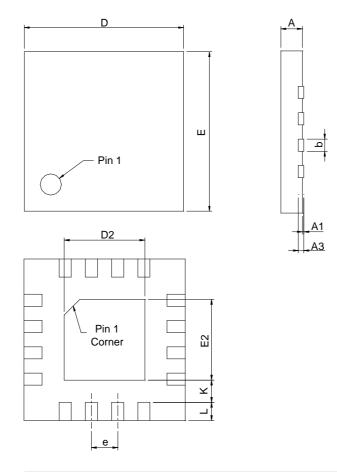

# Package Information

TQFN4x4-16

| Ş       |        | TQFN4x4-16 |       |       |  |  |  |

|---------|--------|------------|-------|-------|--|--|--|

| SY MBOL | MILLIM | ETERS      | INC   | HES   |  |  |  |

| L<br>L  | MIN.   | MAX.       | MIN.  | MAX.  |  |  |  |

| А       | 0.70   | 0.80       | 0.028 | 0.031 |  |  |  |

| A1      | 0.00   | 0.05       | 0.000 | 0.002 |  |  |  |

| A3      | 0.20   | REF        | 0.008 | B REF |  |  |  |

| b       | 0.25   | 0.35       | 0.010 | 0.014 |  |  |  |

| D       | 3.90   | 4.10       | 0.154 | 0.161 |  |  |  |

| D2      | 1.90   | 2.10       | 0.075 | 0.083 |  |  |  |

| E       | 3.90   | 4.10       | 0.154 | 0.161 |  |  |  |

| E2      | 1.90   | 2.10       | 0.075 | 0.083 |  |  |  |

| е       | 0.65   | BSC        | 0.026 | 6 BSC |  |  |  |

| L       | 0.40   | 0.50       | 0.016 | 0.020 |  |  |  |

| К       | 0.20   |            | 0.008 |       |  |  |  |

# **Carrier Tape & Reel Dimensions**

| Application | Α                 | Н                 | T1                 | С                  | d        | D                 | W                  | E1                 | F                  |

|-------------|-------------------|-------------------|--------------------|--------------------|----------|-------------------|--------------------|--------------------|--------------------|

|             | 330.0 ₽.00        | 50 MIN.           | 12.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 12.0 <b>±</b> 0.30 | 1.75 <b>±</b> 0.10 | 5.5 <b>±</b> 0.10  |

| QFN5x5-16   | P0                | P1                | P2                 | D0                 | D1       | Т                 | A0                 | B0                 | K0                 |

|             | 4.0 <b>±</b> 0.10 | 8.0 <b>±</b> 0.10 | 2.0 <b>±</b> 0.10  | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.40 | 5.35 <b>±</b> 0.20 | 5.35 <b>±</b> 0.20 | 1.30 <b>±</b> 0.20 |

| Application | Α                 | Н                 | T1                 | С                  | d        | D                 | W                  | E1                 | F                  |

|             | 330.0 ⊉.00        | 50 MIN.           | 12.4+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 12.0 <b>±</b> 0.30 | 1.75 <b>±</b> 0.10 | 5.5 <b>±</b> 0.05  |

| TQFN4x4-16  | P0                | P1                | P2                 | D0                 | D1       | Т                 | A0                 | B0                 | K0                 |

|             | 4.0 <b>±</b> 0.10 | 8.0 ±0.10         | 2.0 <b>±</b> 0.05  | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.40 | 4.30 <b>±</b> 0.20 | 4.30 <b>±</b> 0.20 | 1.30 <b>±</b> 0.20 |

(mm)

### **Devices Per Unit**

| Package Type | Unit        | Quantity |

|--------------|-------------|----------|

| QFN5x5-16    | Tape & Reel | 2500     |

| TQFN4x4-16   | Tape & Reel | 3000     |

Copyright  $\circledcirc$  ANPEC Electronics Corp. Rev. A.5 - Apr., 2009

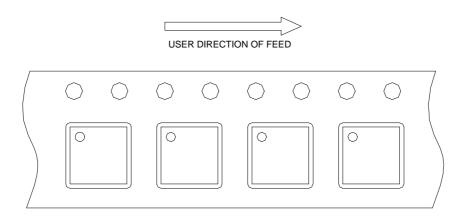

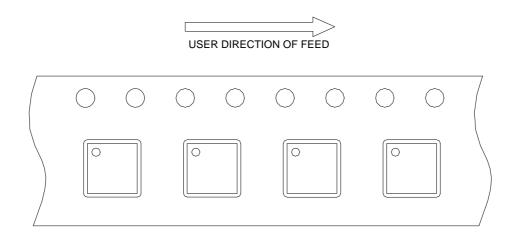

# **Taping Direction Information**

QFN5x5-16

#### TQFN4x4-16

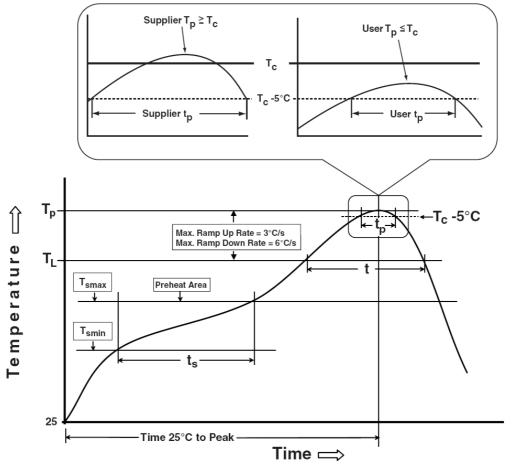

## **Classification Profile**

## **Classification Reflow Profiles**

| Profile Feature                                                                                                                                                               | Sn-Pb Eutectic Assembly                                                                  | Pb-Free Assembly                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------|

| <b>Preheat &amp; Soak</b><br>Temperature min (T <sub>smin</sub> )<br>Temperature max (T <sub>smax</sub> )<br>Time (T <sub>smin</sub> to T <sub>smax</sub> ) (t <sub>s</sub> ) | 100 °C<br>150 °C<br>60-120 seconds                                                       | 150 °C<br>200 °C<br>60-120 seconds |

| Average ramp-up rate<br>(T <sub>smax</sub> to T <sub>P</sub> )                                                                                                                | 3 °C/second max.                                                                         | 3°C/second max.                    |

| Liquidous temperature (T <sub>L</sub> )<br>Time at liquidous ( $t_L$ )                                                                                                        | 183 °C<br>60-150 seconds                                                                 | 217 °C<br>60-150 seconds           |

| Peak package body Temperature (T <sub>p</sub> )*                                                                                                                              | See Classification Temp in table 1                                                       | See Classification Temp in table 2 |

| Time $(t_P)^{**}$ within 5°C of the specified classification temperature $(T_c)$                                                                                              | 20** seconds                                                                             | 30** seconds                       |

| Average ramp-down rate ( $T_p$ to $T_{smax}$ )                                                                                                                                | 6 °C/second max.                                                                         | 6 °C/second max.                   |

| Time 25°C to peak temperature                                                                                                                                                 | 6 minutes max.                                                                           | 8 minutes max.                     |

|                                                                                                                                                                               | ure $(T_p)$ is defined as a supplier minimu nperature $(t_p)$ is defined as a supplier n |                                    |

### **Classification Reflow Profiles (Cont.)**

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br><sup>3</sup> 350 |

|----------------------|--------------------------------|--------------------------------------------|

| <2.5 mm              | 235 °C                         | 220 °C                                     |

| ≥2.5 mm              | 220 °C                         | 220 °C                                     |

Table 2. Pb-free Process – Classification Temperatures (Tc)

| Package<br>Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup><br>>2000 |

|----------------------|--------------------------------|------------------------------------|---------------------------------|

| <1.6 mm              | 260 °C                         | 260 °C                             | 260 °C                          |

| 1.6 mm – 2.5 mm      | 260 °C                         | 250 °C                             | 245 °C                          |

| ≥2.5 mm              | 250 °C                         | 245 °C                             | 245 °C                          |

## **Reliability Test Program**

| Test item     | Method             | Description                  |

|---------------|--------------------|------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                 |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ 125°C       |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C |

| тст           | JESD-22, A104      | 500 Cycles, -65°C~150°C      |

| ESD           | MIL-STD-883-3015.7 | VHBM 2KV, VMM 200V           |

| Latch-Up      | JESD 78            | 10ms, 1 <sub>tr</sub> 100mA  |

### **Customer Service**

#### Anpec Electronics Corp.

Head Office :

No.6, Dusing 1st Road, SBIP, Hsin-Chu, Taiwan, R.O.C. Tel: 886-3-5642000 Fax: 886-3-5642050

Taipei Branch : 2F, No. 11, Lane 218, Sec 2 Jhongsing Rd., Sindian City, Taipei County 23146, Taiwan Tel : 886-2-2910-3838 Fax : 886-2-2917-3838